[PDF] Jacinto 7 LPDDR4 Board Design and Layout Guidelines (Rev. F): Expert Tips! High current pcb layout guidelines

Ah, so you want to design a PCB for external memory, eh? Very good, very good. It's not just about slapping down components and hoping for the best. Need some discipline, some finesse, like perfecting the art of calligraphy. A sloppy layout? That's like writing with a blunt brush! Let’s see what we can do, shall we?

First, the Write Leveling – It's Crucial!

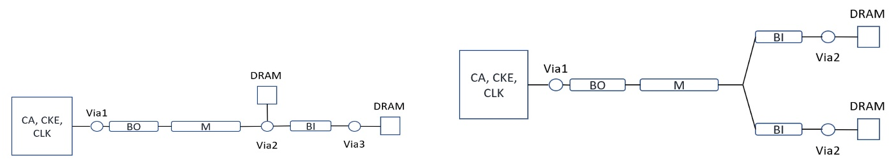

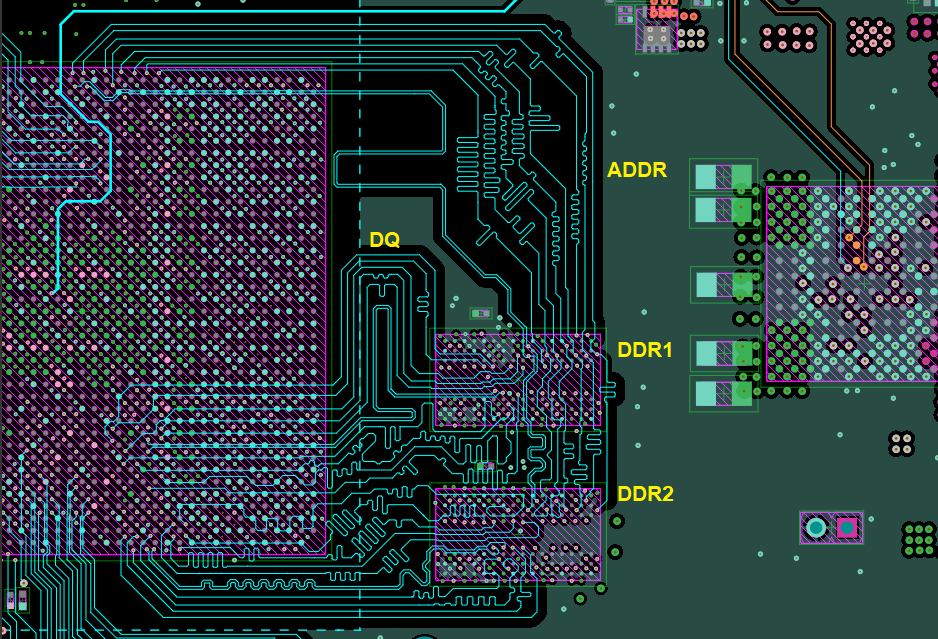

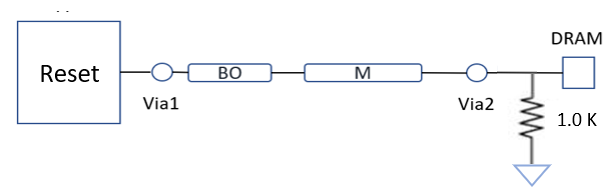

Okay, okay, pay close attention now. Write leveling in your DDR memory is important. It’s like balancing a stack of delicate porcelain teacups. If one is off, the whole thing comes crashing down! So, what is write leveling? It’s making sure the data arrives at the memory chips at the right time, no early, no late. Imagine a group of people trying to clap in unison, some are too eager and clap ahead of everyone else, some are slow and clap late. It's a mess! Write leveling aligns everything. The signals must be precisely timed so the data is written correctly. Consider trace lengths! Longer traces introduce delays. Make sure your signals traveling to the memory devices are matched in length. You want symmetry, like a well-balanced bonsai tree. Don’t cut corners here, use software to help you calculate the delays, and simulate the performance. Think of it as meticulously planning a complex tea ceremony – everything must be perfect.

Now, the PCB Design Rules and Tips – Golden Rules, Follow Them!

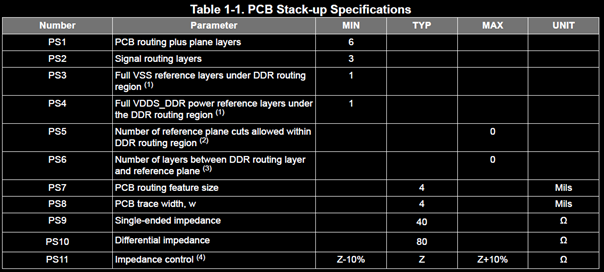

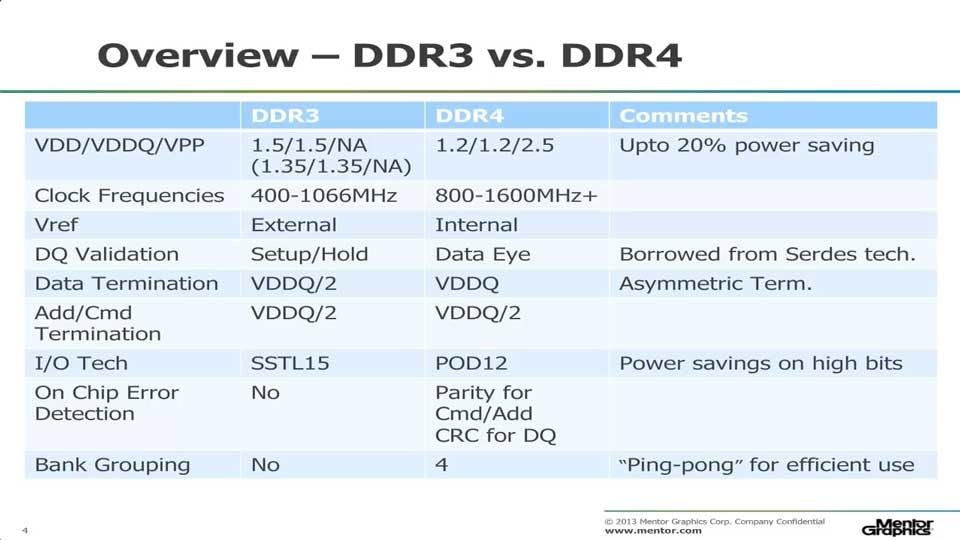

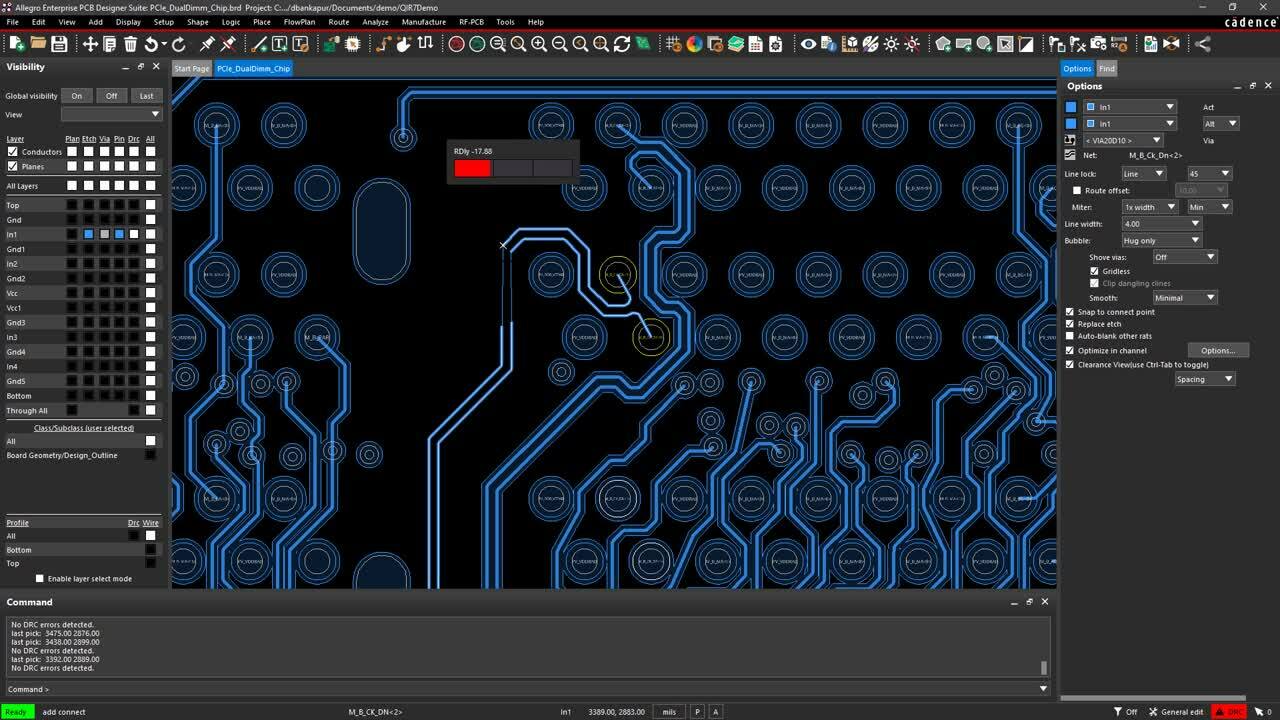

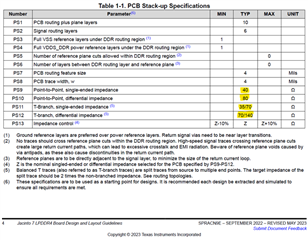

These rules, they are not just suggestions, you know? They are the foundation, the bedrock, upon which your successful PCB is built! Think of it like the secret family recipe for the perfect dumplings. If you skip an ingredient, the whole flavor is ruined! Consider your power and ground planes. These are essential. They are like the strong, steady roots of a tree, providing nourishment and stability. Use solid, unbroken planes. Minimize the number of vias that disrupt the planes. Vias, they can be necessary, but they also introduce impedance discontinuities, like pebbles in a smooth stream. And impedance matching! This is paramount. You want to make sure the impedance of your traces matches the impedance of the memory and the controller. Reflections, oh, those are nasty! They can corrupt your signals and lead to all sorts of problems. Treat them like unwelcome guests. Terminate the traces properly to prevent reflections. Also, routing! Keep your traces short and direct. Avoid sharp bends. Think of it like a smooth, flowing river. Sharp bends create turbulence and disrupt the flow. Route your differential pairs close together. They are like a pair of chopsticks, working together in perfect harmony. Shield sensitive signals. Protect them from noise and interference. Imagine you are wrapping delicate treasures in silk cloth to keep them safe. Finally, decoupling capacitors! Use plenty of them. Place them close to the memory chips. They provide local charge storage and help to reduce noise on the power rails. They are like little batteries, always ready to supply power when needed. Remember all these points, and your PCB design will be a masterpiece! Like a perfectly brewed cup of jasmine tea.

If you are looking for AM6412: EVM的LPDDR4 layout design確認 - 处理器论坛 - 处理器 - E2E™ 设计支持 you've came to the right page. We have 25 Pics about AM6412: EVM的LPDDR4 layout design確認 - 处理器论坛 - 处理器 - E2E™ 设计支持 like (PDF) Jacinto 7 LPDDR4 Board Design and Layout Guidelines (Rev. B, pcb design layout guidelines Pcb layout guidelines for design and also TDA4VH-Q1: LPDDR4 layout - Processors forum - Processors - TI E2E. Read more:

AM6412: EVM的LPDDR4 Layout Design確認 - 处理器论坛 - 处理器 - E2E™ 设计支持

e2echina.ti.com

e2echina.ti.com LPDDR4 Ug583 Ultrascale PCB Design | PDF | Computer Data | Electronic

www.scribd.com

www.scribd.com (PDF) Board Design Layout Guidelines; External Memory … · Introduce The

dokumen.tips

dokumen.tips Nine Dot Connects » DDR3, DDR4, LPDDR4 Design And Layout Services, Nine

www.ninedotconnects.com

www.ninedotconnects.com ddr3 layout design ddr4 services ddr

5.3. LPDDR4 Interface Design Guidelines

www.intel.com

www.intel.com TDA4VH-Q1: LPDDR4 Layout - Processors Forum - Processors - TI E2E

e2e.ti.com

e2e.ti.com China Mobile DDR4 Lpddr4 Pcb Design And Layout Guidelines Socket

www.chinax.com

www.chinax.com PCB Routing Guidelines For DDR4 Memory Devices And Impedance | Blog

resources.altium.com

resources.altium.com DDR4 And LPDDR4 - Board Design Verification And Challenges - Mentor

www.mentor.com

www.mentor.com ddr4 lpddr4 verification counterparts demand dive pcb

TI's Jacinto 7 Processors Enable Automotive ADAS And Gateway

embeddedcomputing.com

embeddedcomputing.com jacinto

Lpddr4-test-board/lpddr4-test-board.pdf At Main · Antmicro/lpddr4-test

Nine Dot Connects » DDR3, DDR4, LPDDR4 Design And Layout Services, Nine

www.ninedotconnects.com

www.ninedotconnects.com design ddr3 layout services ddr banks signals pairs gbps large nine dot connects

(PDF) Jacinto 7 LPDDR4 Board Design And Layout Guidelines (Rev. B

dokumen.tips

dokumen.tips TDA4VH-Q1: LPDDR4 Layout - Processors Forum - Processors - TI E2E

e2e.ti.com

e2e.ti.com Nine Dot Connects » DDR3, DDR4, LPDDR4 Design And Layout Services, Nine

www.ninedotconnects.com

www.ninedotconnects.com fly ddr3 route example ddr4

Pcb Routing Guidelines - Design Talk

design.udlvirtual.edu.pe

design.udlvirtual.edu.pe 5.3. LPDDR4 Interface Design Guidelines

www.intel.com

www.intel.com TDA4VH-Q1: LPDDR4 Layout - Processors Forum - Processors - TI E2E

e2e.ti.com

e2e.ti.com China Mobile DDR4 Lpddr4 Pcb Design And Layout Guidelines Socket

www.chinax.com

www.chinax.com High Current Pcb Layout Guidelines - Design Talk

design.udlvirtual.edu.pe

design.udlvirtual.edu.pe PCB Design Rules And Tips

www.6pcb.com

www.6pcb.com Pcb Design Layout Guidelines Pcb Layout Guidelines For Design

High Speed Pcb Layout Guidelines - Design Talk

design.udlvirtual.edu.pe

design.udlvirtual.edu.pe Nine Dot Connects » DDR3, DDR4, LPDDR4 Design And Layout Services, Nine

www.ninedotconnects.com

www.ninedotconnects.com ddr3 design serpentines layout ddr tuning employed assist match length ddr4

TDA4VM-Q1: Is A Deviation From SPRACN9E (LPDDR4 Board Design Guidelines

e2e.ti.com

e2e.ti.com Ti's jacinto 7 processors enable automotive adas and gateway. Nine dot connects » ddr3, ddr4, lpddr4 design and layout services, nine. 5.3. lpddr4 interface design guidelines